场景

很多初学者看到板上只有一个25Mhz时钟或者固定时钟的时候,都会疑惑,时钟怎么是改变?如果要在更大时钟频率工作怎么办?其实在很多FPGA芯片内部都集成了PLL,其他厂商可能不叫PLL,但是也有类似的功能模块,通过PLL可以倍频分频,产生其他很多时钟。

vivado中分频ip核

平台 vavado2019.2

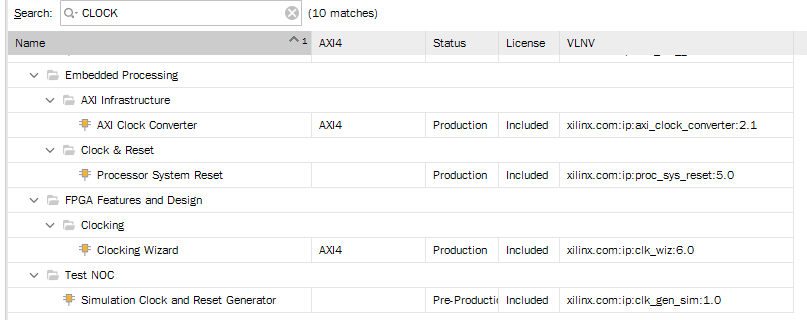

添加ip核 clocking wizard

ip核介绍

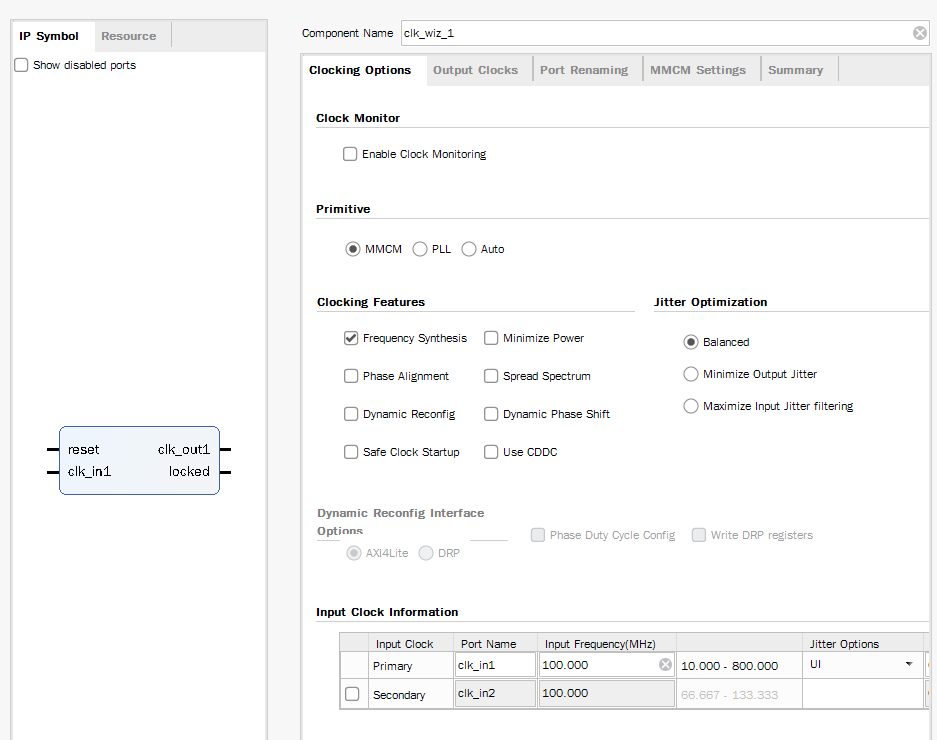

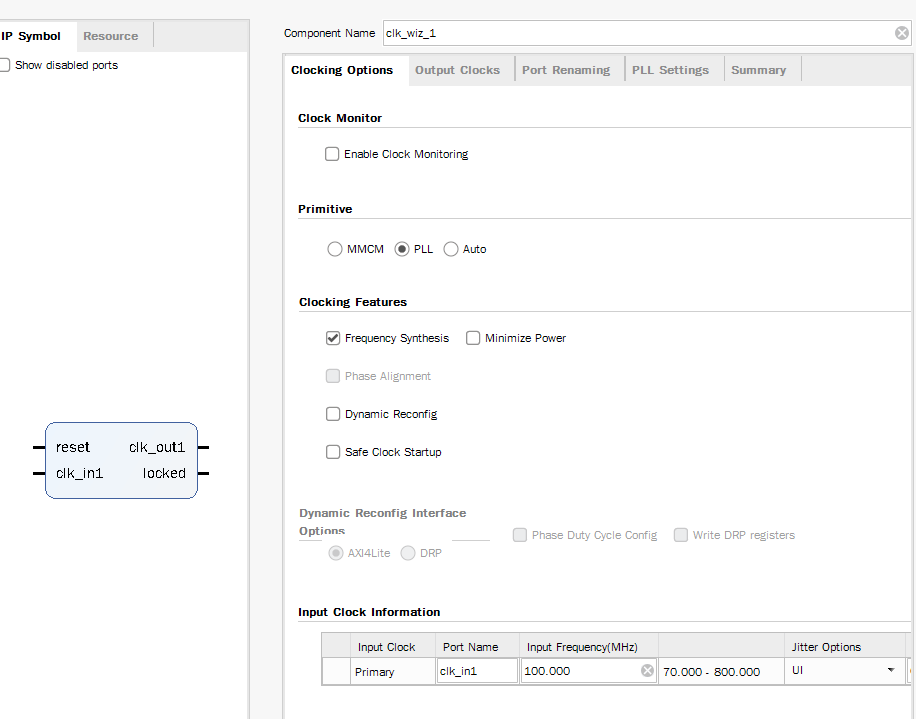

pll与mmcm

PLL(phase-locked loop),即锁相环,主要用于频率综合,可以从一个输入时钟信号生成多个时钟信号。MMCM用于在与给定输入时钟有设定的相位和频率关系的情况下,生成不同的时钟信号。

frequency synthesis:频率合成允许输出时钟与活动输入时钟具有不同的频率。

spread spectrum:扩频提供调制输出时钟,这降低了电子设备产生的电磁干扰的频谱密度。此功能仅适用于MMCM(E2/E3/E4)_ADV原语。该特性的UNISIM模拟支持目前不可用。

Phase ALIGNMENT:相位校准允许输出时钟锁相到一个基准电压源,例如器件的输入时钟引脚。

minimaze power:最小化能量可以让你最小化元素所需的能量。这可能以频率、相位偏移或占空比精度为代价。

Dynamic Phase Shif::动态相移允许您更改输出时钟的相位关系。

Dynamic Reconfiguration:动态重新配置允许您在设备配置后更改原语的编程。选择此选项时,默认情况下选择AX4-Lite接口来重新配置时钟原语。

Balanced:选择“平衡”会导致软件为抖动优化选择正确的带宽。

Minimize Output Jitte:最小化输出抖动。该特性可最大限度地降低输出时钟的抖动,但代价是功耗和可能的输出时钟相位误差。此功能不适用于最大化输入抖动过滤功能。

Maximize Input Jitter filtering:最大化输入抖动滤波允许输入时钟有更大的输入抖动,但会对输出时钟的抖动产生负面影响。此功能不适用于最小化输出抖动功能。

Safe Clock Startup and Sequencing:安全时钟启动和时序控制可用于在输出端获得稳定有效的时钟。它还按照配置中指定的特定顺序启用时钟。

Clock Monitor:时钟监视器帮助您监视时钟向导的时钟输入。它可以监控多达四个时钟。您可以监控输入频率是否超出预期频率范围,并检测时钟停止和时钟故障。

Auto Primitive:自动原语为您的需求实例化适当的时钟原语。您不需要知道MMCM或锁相环的规格来判断哪一个原语适合您的要求;向导会为您执行此操作。此功能仅适用于超大规模和超大规模+设备。

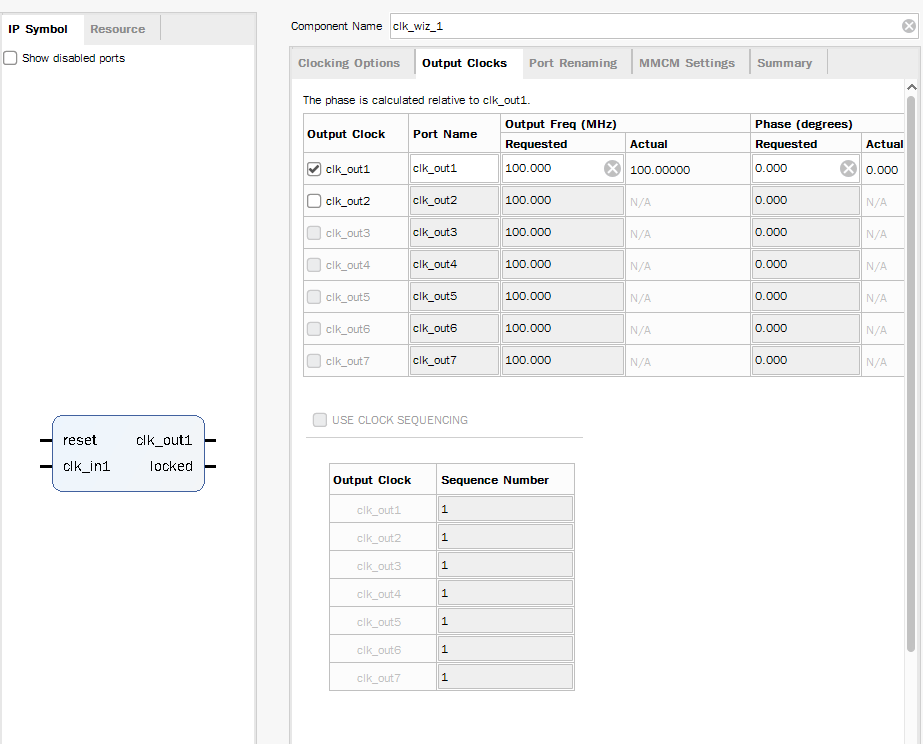

output clocks

在output块改变输出时钟即可